Designing for testability in the realm of VLSI (Very Large Scale Integration) is a crucial aspect of the semiconductor design process. Testability refers to the overall ease with which a VLSI circuit can get tested for manufacturing defects or even any sort of faults. It encompasses incorporating design techniques and features that allow efficient and accurate testing, which is crucial for ensuring the reliability and overall functionality of complex integrated circuits. Since it is the era of advanced VLSI, you have to be careful about each and every single aspect. This post is sharing with you the top five tips to design for testability in VLSI.

Table of Contents

Design for Controllability & Observability

Controllability and observability are the main factors in designing for testability. Controllability refers to the capability to set specific inputs to the circuit, while observability refers to the overall ability to observe and measure the outputs. To boost overall controllability, it is critical to provide test access to internal signals and enable the selective control of different circuit elements. This can get accomplish by incorporating scan chains that permit the serial shifting of test patterns into the circuit. Similarly, it is also important for you to know that you can improve observability by introducing scan flip-flops that capture the internal state of the circuit during overall testing. By enhancing controllability and observability, the testability of the VLSI circuit is massively improve.

Use Built-In Self-Test (BIST) methods

Built-In Self-Test (BIST) methods are an effective way to enhance the testability of VLSI circuits. BIST includes integrating self-test circuitry inside the design that permits on-chip testing without the requirement for external test equipment. BIST can include diverse types of components, such as test pattern generators, signature analysers, and response compressors. Test pattern generators produce the test vectors that are essential to stimulate the circuit, while signature analysers compare the expected responses with the actual responses to recognize faults. Response compressors reduce the size of the signature to minimise storage requirements. By including BIST techniques, the testability of the VLSI circuit is massively improve, reducing test time and even costs.

Implement Error Correction Codes (ECC)

now, since you are in this field, you should also know that error Correction Codes (ECC) are massively used in VLSI designs to detect and even correct errors that may emerge during testing or operation. ECC adds overall redundancy to the data transmitted or stored, permitting the detection and correction of errors. By incorporating ECC, it turns out to be possible to identify and correct faults in the circuit, boosting its testability. Commonly used ECC schemes include Hamming codes, proper Reed-Solomon codes, and Bose-Chaudhuri-Hocquenghem (BCH) codes. The selection of the right and appropriate ECC scheme relies totally on the specific requirements of the VLSI design, like the desired error-detection capability and even overhead constraints. Whether it is about VLSI design automation or anything else, the reduction of errors is a must.

Partition Design for Modular Testing

Well, partitioning the overall VLSI design into smaller, modular blocks is an effective and powerful strategy for boosting the overall testability. By breaking down the design into numerous manageable units, it turns out to be easier for you to test each module individually, reducing the complexity of the general testing process. Modular testing permits the detection and isolation of faults at the module level, allowing faster debugging and reducing the influence of faults on the overall system. Additionally, you know modular testing facilitates reusability, as authenticate modules can get reuse in different designs, saving time and even effort in the phase of testing.

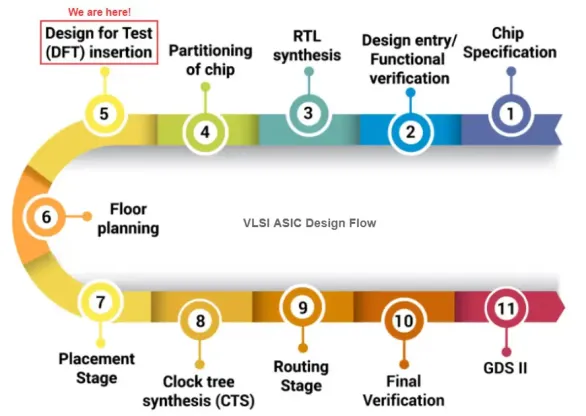

Perform Design for Testability (DFT) Supplement

Design for Testability (DFT) supplement involves the inclusion of specific testability features during the overall design process. DFT techniques try to improve the overall observability and controllability of the circuit, making it convenient to test. Some commonly used DFT methods can be like or include boundary scan (IEEE 1149.1), that permits access to internal signals for testing through a standardised and proper interface; memory built-in self-test (MBIST), which eases the testing of memories embedded in the overall VLSI design. Apart from these top tips, there are some more points that you should know for better understanding.

Hierarchical Design

Hierarchical design is a top-down type of design approach that breaks down the VLSI circuit into manifold hierarchical levels, such as subsystems, blocks, and proper sub-blocks. Each level can get test independently, allowing for efficient testing at diverse types of levels of hierarchy. This approach abridges the testing process by concentrating on smaller, manageable units and allows parallel testing of diverse modules. Hierarchical design even facilitates easier debugging and maintenance, as faults can get localise to particular levels or modules.

Include Testability Constraints Early in the Design Cycle

Designing for testability must begin early in the design cycle to make sure that testability constraints are consider and incorporated from the beginning. By defining testability requirements and constraints at an early phase or stage, being designers, you can make informed decisions regarding design trade-offs and select appropriate test structures and even proper techniques. This proactive approach reduces the need for redesign and dodges costly modifications later in the design process.

Optimise Test Point Placement

Test point placement means the strategic placement of test access mechanisms, such as scan chains or even boundary scan cells, within the VLSI circuit. Optimize test point placement simply aims to minimize the number of test points that are require while maximising test coverage. Careful consideration should be give to the placement of test points to make sure that critical circuit elements are adequately. And properly covered and faults can be quickly and conveniently detected and isolated. Making use of automated tools and algorithms can help in optimising test point placement.

Utilize Fault Simulation & Diagnosis

Then you know fault simulation and diagnosis are essential methods for identifying and locating faults in the VLSI circuit. Fault simulation includes simulating the behavior of the circuit under diverse fault conditions to evaluate the effectiveness of the test patterns and even to estimate the fault coverage. Fault diagnosis tries to identify the specific location of the faults inside the circuit. These techniques help you in improving testability by identifying weak areas in the design and permitting targeted improvements.

Conclusion

To sum up, whether pcb engineering or any other similar tasks of designing, having the right tips on your side can only make things better, more effective and more productive for you.